# NTE7483 Integrated Circuit TTL – 4-Bit Binary Full Adder with Fast Carry

#### **Description:**

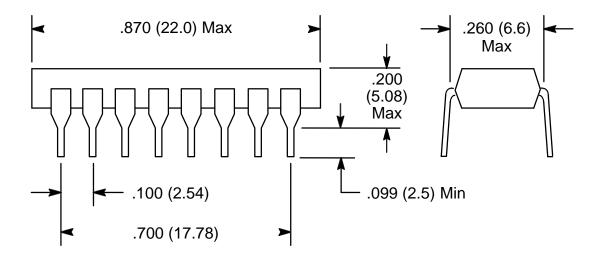

The NTE7483 is a 4-bit binary full adder in a 16-Lead plastic DIP type package that performs the addition of two 4-bit binary numbers. The sum  $(\Sigma)$  outputs are provided for each bit and the resultant carry (C4) is obtained from the fourth bit. This device features full internal look-ahead across all four bits generating the carry term in ten nanoseconds (typ). This capability provides the system designer with partial look-ahead performance at the economy and reduced package count of a ripply-carry implementation.

The adder logic, including the carry, is implemented in its true form. End around carry can be accomplished without the need for logic or level inversion.

#### Features:

- Full-Carry Look-Ahead Across the Four Bits

- Systems Achieve Partial Look-Ahead Performance with the Economy of Ripple-Carry

- The NTE74283 is Recommended for New Design as it Features Supply Voltage and GND on Corner Pins to Simplify Board Layout.

#### Absolute Maximum Ratings: (Note 1)

| Supply Voltage, V <sub>CC</sub> 7                          | V      |

|------------------------------------------------------------|--------|

| Input Voltage, V <sub>IN</sub> 5.5 <sup>v</sup>            | V      |

| Interemitter Voltage (Note 2) 5.5                          | V      |

| Operating Temperature Range, T <sub>A</sub> 0°C to +70°C   | С      |

| Storage Temperature Range, T <sub>stg</sub> 65°C to +150°C | $\Box$ |

Note 1. Unless otherwise specified, all voltages are referenced to GND.

Note 2. This is the voltage between two emitters of a multiple-emitter transistor. This rating applies between the following pairs: A1 and B1, A and B2, A3 and B3, A4 and B4.

## **Recommended Operating Conditions:**

| Parameter                                      | Symbol          | Min  | Тур | Max  | Unit |

|------------------------------------------------|-----------------|------|-----|------|------|

| Supply Voltage                                 | V <sub>CC</sub> | 4.75 | 5.0 | 5.25 | V    |

| High-Level Output Current Any Output Except C4 | I <sub>OH</sub> | _    | _   | -800 | μΑ   |

| Output C4                                      |                 | _    | _   | -400 | μΑ   |

| Low-Level Output Current Any Output Except C4  | I <sub>OL</sub> | _    | _   | 16   | mA   |

| Output C4                                      |                 | _    | _   | 8    | mA   |

| Operating Temperature Range                    | T <sub>A</sub>  | 0    | _   | +70  | °C   |

## **Electrical Characteristics**: (Note 3, Note 4)

| Parameter                                            | Symbol          | Test Conditions                                                   | Min | Тур | Max  | Unit |

|------------------------------------------------------|-----------------|-------------------------------------------------------------------|-----|-----|------|------|

| High Level Input Voltage                             | $V_{IH}$        |                                                                   | 2   | _   | -    | V    |

| Low Level Input Voltage                              | $V_{IL}$        |                                                                   | -   | _   | 0.8  | V    |

| Input Clamp Voltage                                  | $V_{IK}$        | $V_{CC} = MIN, I_I = -12mA$                                       | -   | -   | -1.5 | V    |

| High Level Output Voltage                            | V <sub>OH</sub> | $V_{CC} = MIN$ , $V_{IH} = 2V$ , $V_{IL} = 0.8V$ , $I_{OH} = MAX$ | 2.4 | 3.4 | _    | V    |

| Low Level Output Voltage                             | V <sub>OL</sub> | $V_{CC} = MIN, V_{IH} = 2V, V_{IL} = 0.8V, I_{OL} = 4mA$          | -   | 0.2 | 0.4  | V    |

| Input Current                                        | ΙĮ              | V <sub>CC</sub> = MAX, V <sub>I</sub> = 5.5V                      | _   | _   | 1    | mA   |

| High Level Input Current                             | I <sub>IH</sub> | $V_{CC} = MAX, V_I = 2.4V$                                        | -   | _   | 40   | μΑ   |

| Low Level Input Current                              | I <sub>IL</sub> | $V_{CC} = MAX, V_I = 0.4V$                                        | -   | _   | -1.6 | mΑ   |

| Short-Circuit Output Current<br>Any Output Except C4 | I <sub>OS</sub> | V <sub>CC</sub> = MAX, Note 5                                     | -18 | _   | -55  | mA   |

| Output C4                                            |                 |                                                                   | -18 | _   | -70  | mΑ   |

| Supply Current All B Low, Other Inputs at 4.5V       | I <sub>CC</sub> | V <sub>CC</sub> = MAX, Outputs Open                               | _   | 56  | _    | mA   |

| All Inputs at 4.5V                                   |                 |                                                                   | -   | 66  | 110  | mΑ   |

- Note 3. .For conditions shown as MIN or MAX, use the appropriate value specified under "Recommended Operation Conditions".

- Note 4. All typical values are at  $V_{CC} = 5V$ ,  $T_A = +25^{\circ}C$ . Note 5. Not more than one output should be shorted at a time.

## **Switching Characteristics**: $(V_{CC} = 5V, R_L = 667\Omega, T_A = +25^{\circ}C)$ unless otherwise specified)

| Parameter                                                  | Symbol           | Test Conditions                  | Min | Тур | Max | Unit |

|------------------------------------------------------------|------------------|----------------------------------|-----|-----|-----|------|

| Propagation Delay Time                                     | t <sub>PLH</sub> | $R_L = 400\Omega$ , $C_L = 15pF$ | -   | 14  | 21  | ns   |

| (From C0 Input to Any $\Sigma$ Output)                     | t <sub>PHL</sub> |                                  | _   | 12  | 21  | ns   |

| Propagation Delay Time                                     | t <sub>PLH</sub> |                                  | _   | 16  | 24  | ns   |

| (From $A_i$ or $B_i$ Input to $\Sigma_i$ Output)           | t <sub>PHL</sub> |                                  | _   | 16  | 24  | ns   |

| Output Enable Time                                         | t <sub>PZH</sub> | $R_L = 780\Omega, C_L = 15pF$    | _   | 9   | 14  | ns   |

| (From C0 Input to C4 Output)                               | t <sub>PZL</sub> |                                  | _   | 11  | 16  | ns   |

| Propagation Delay Time                                     | t <sub>PLH</sub> |                                  | _   | 9   | 14  | ns   |

| (From A <sub>i</sub> or B <sub>i</sub> Input to C4 Output) | t <sub>PHL</sub> |                                  | _   | 11  | 16  | ns   |

## **Function Table:**

|          |          |          |          | Output      |                       |                |             |                       |                |

|----------|----------|----------|----------|-------------|-----------------------|----------------|-------------|-----------------------|----------------|

|          | Inp      | out      |          | When C0 = L |                       | When<br>C2 = L | When C0 = H |                       | When<br>C2 = H |

| A1<br>A3 | B1<br>B3 | A2<br>A4 | B2<br>B4 | Z1 Z3       | Z <b>2</b> Z <b>4</b> | C2<br>C4       | Z1 Z3       | Z <b>2</b> Z <b>4</b> | C2<br>C4       |

| L        | L        | L        | L        | L           | L                     | L              | Н           | L                     | L              |

| Н        | L        | L        | L        | Н           | L                     | L              | L           | Н                     | L              |

| L        | Н        | L        | L        | Н           | L                     | L              | L           | Н                     | L              |

| Н        | Н        | L        | L        | L           | Н                     | L              | Н           | Н                     | L              |

| L        | L        | Н        | L        | L           | Н                     | L              | Н           | Н                     | L              |

| Н        | L        | Н        | L        | Н           | Н                     | L              | L           | L                     | Н              |

| L        | Н        | Н        | L        | Н           | Н                     | L              | L           | L                     | Н              |

| Н        | I        | Η        | L        | L           | L                     | Н              | I           | L                     | Ι              |

| L        | L        | L        | Η        | L           | Ι                     | L              | I           | Ι                     | L              |

| Н        | L        | L        | Н        | Н           | Н                     | L              | L           | L                     | Н              |

| L        | Η        | L        | Н        | Н           | Н                     | L              | L           | L                     | Н              |

| Н        | Н        | L        | Н        | L           | L                     | Н              | Н           | L                     | Н              |

| L        | L        | Н        | Н        | L           | L                     | Н              | Н           | L                     | Н              |

| Н        | L        | Н        | Н        | Н           | L                     | Н              | L           | Н                     | Н              |

| L        | Н        | Н        | Н        | Н           | L                     | Н              | L           | Н                     | Н              |

| Н        | Η        | Н        | Н        | L           | Н                     | Н              | Η           | Н                     | Н              |

H = HIGH Level

L = LOW Level

NOTE: Input conditions at A1, B1, A2, B2, and C0 are used to determine outputs  $\Sigma$ 1 and  $\Sigma$ 2 and the value of the internal carry C2. The values at C2, A3, B3, A4, and B4 are then used to determine outputs  $\Sigma$ 3,  $\Sigma$ 4, and C4.

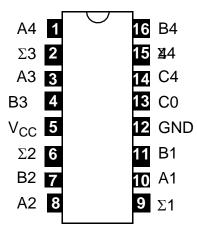

# **Pin Connection Diagram**